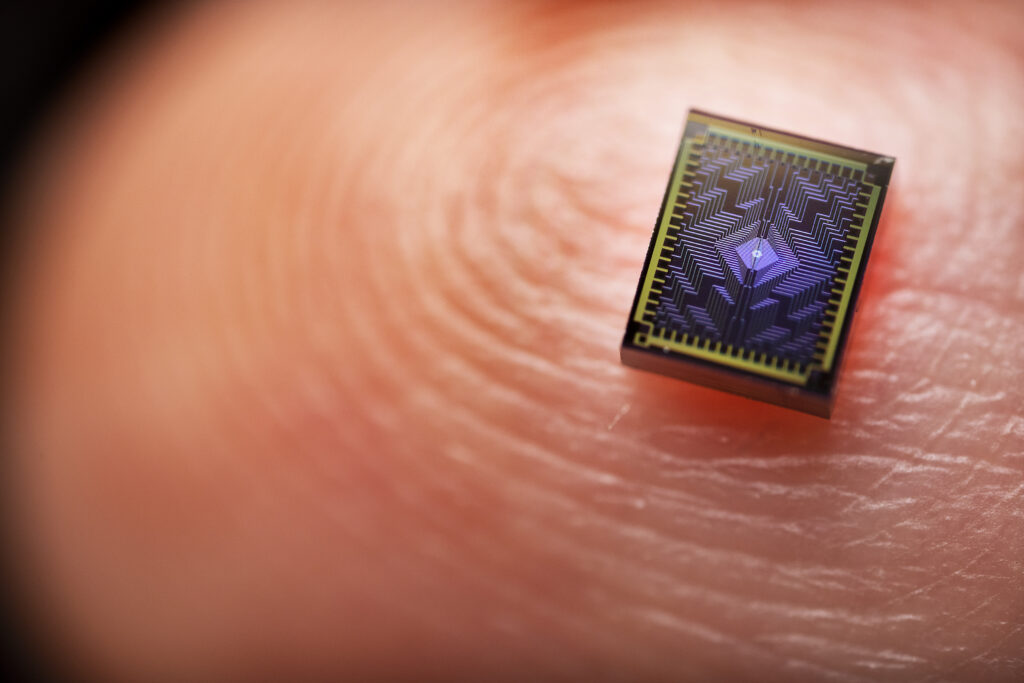

1.4nmプロセスで3大ファウンドリーが異なる戦略

TSMCが先行、インテルは戦略転換、サムスンは量産延期

世界最先端半導体技術の1.4ナノメートル(nm)プロセスを巡る競争が激化する中、世界の主要半導体受託生産(ファウンドリー)世界大手の台湾積体電路製造(TSMC、台積電)、Intel(インテル)、サムスン電子の3社がそれぞれ異なる戦略を打ち出している。TSMCは2028年の量産を目指して計画通り開発を推進し、インテルは既存の1.8nm「Intel 18A」から1.4nm「Intel 14A」へ戦略をシフト。一方でサムスンは財務上の制約から、1.4nmプロセスの量産開始を29年に延期する方針を明らかにした。

TSMCは、次世代「14A(1.4nm)」プロセスの開発を順調に進めており、28年の量産開始目標を維持している。このプロセスは第2世代ナノシートトランジスタとNanoFlex Pro標準セル構造を採用し、同等電力で最大15%の速度向上、同等性能で最大30%の消費電力削減、そして論理密度は1.2倍になるとされている。TSMCは常に技術導入に慎重な姿勢を貫いており、未検証の新技術を同時導入しないことで、歩留まり向上までの期間を短縮し、量産時の安定性と供給効率を確保する戦略を取っている。

一方、インテルは苦境の中で戦略を大きく見直している。リップブー・タン(Lip-Bu Tan、陳立武)最高経営責任者(CEO)は、従来重視されていたIntel 18Aから14Aへの転換を検討しており、前CEOのパット・ゲルシンガー氏が推進した18Aプロセスの方針を見直す構えだ。18AではRibbonFETやPowerViaといった先進技術を導入しているが、社内製品向けが中心で外部顧客への訴求力は限定的とされる。Intel 14Aは2027年にリスク試作開始予定で、第2世代のGAA(Gate-All-Around)「RibbonFET 2」および背面電源ネットワーク(PowerDirect)を採用し、Turbo Cellsにより性能と電力効率の強化を図る。これにより、性能は15〜20%向上、チップ密度は約30%増、消費電力は25%以上削減される見込みだ。

さらに、インテルは次世代露光技術であるHigh NA EUV装置の導入においても先行しており、すでに2台目を設置済み。ただし、こうした先行投資が続く中で、年400億米ドル(約5兆7820億円)を超える巨額の資本支出は財務面に重くのしかかっている。14Aの26年投入計画も、High NA EUVの歩留まり課題が解決するかどうかに左右される見通しで、供給装置が限定的である現状ではなお困難が多い。また、Microsoft(マイクロソフト)の18Aチップは順調に進行している一方で、NVIDIA(エヌビディア)やAMDなどAI(人工知能)分野の主要プレイヤーは依然としてTSMCを好んでおり、インテルにとっては14Aで競争力を示すことが急務となっている。

サムスン電子はこのほど、当初2027年に予定していた1.4nmプロセスの量産を29年に延期することを発表。テストラインの立ち上げも年内あるいは来年にずれ込む見通しで、TSMCの計画より1年遅れることになる。この決定は、同社がファウンドリー部門で連続赤字を記録している中での戦略的な方向転換と見られている。23年には同部門で4兆ウォン(約4000億円)、24年第1四半期(1〜3月)にも2兆ウォンの損失を出しており、財務健全性の確保が急務となっていた。

サムスンは1.4nmへの投資を一時停止し、代わりに2nmプロセスの歩留まり向上と既存技術の最適化に注力する方針を示している。現在、サムスンの2nmプロセスの歩留まりは約40%と、TSMCの60%基準には届いていない。これを改善すべく、同社は新型プロセッサ「Exynos 2600」の量産成功に向けた専任プロジェクトチームを設置し、米電気自動車(EV)大手のTesla(テスラ)やQualcomm(クアルコム)など米国の大口顧客からの2nm受注獲得を狙っている。

(500×80px)(450×80px)(460×80px)(470×80px)(2).png)